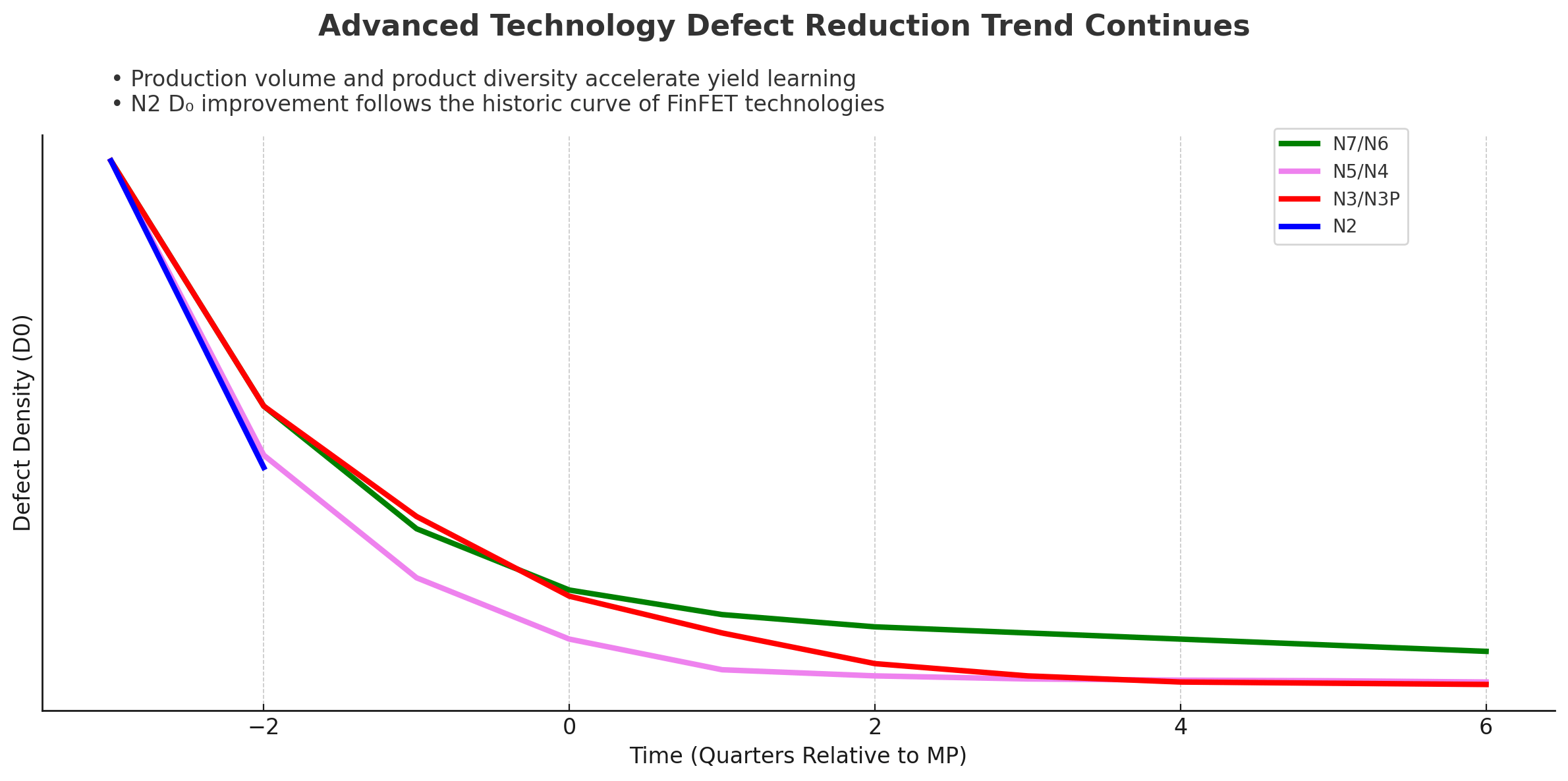

TSMC expuso la densidad de defectos (D0) de su tecnología de proceso N2 en relación con sus predecesores en la misma etapa de desarrollo en su simposio de tecnología de América del Norte esta semana. Según la compañía, la densidad de defectos está por debajo de la de los nodos de fabricación N3, N5 y N7. Además, la diapositiva publicada por ComputerBase revela que N2 está a dos cuartos de la producción en masa, lo que significa que TSMC está en la pista para comenzar a hacer chips de 2 Nm a fines del cuarto trimestre de 2025, como se esperaba.

Aunque el N2 de TSMC es la primera tecnología de proceso de la compañía para adoptar transistores de nanocuos de la puerta de entrada (GAA), el nodo tiene una densidad de defectos más baja que sus predecesores en la misma etapa de desarrollo, dos cuartos antes de la producción en masa (MP). Los predecesores-N3/N3P, N5/N4 y N7/N6-se basaron en transistores FINFET conocidos. Entonces, a pesar de ser el primer nodo de TSMC utilizando transistores de nanocuques de GAA, la densidad de defectos N2 se está volviendo más rápido (bueno, más pronunciada) que la de sus predecesores antes del hito de fabricación de alto volumen (HVM).

La tabla traza la densidad de defectos contra el tiempo, que abarca desde tres cuartos antes de la producción en masa en seis cuartos después de MP. En todos los nodos que se muestran (N7/N6 (verde), N5/N4 (violeta), N3/N3p (rojo) y N2 (azul), las densidades de defectos disminuyen significativamente como rampas de producción, aunque a diferentes tasas dependiendo de la complejidad del nodo. En particular, N5/N4 mostró la reducción de defectos tempranos más agresivos, mientras que N7/N6 mostró una mejora de rendimiento más gradual. La curva N2 comienza con niveles de defectos iniciales más altos que N5/N4 pero disminuye bruscamente, coincidiendo estrechamente con la trayectoria de reducción de defectos de N3/N3p.

La diapositiva enfatiza que el volumen de producción y la diversidad de productos siguen siendo los impulsores clave para acelerar las mejoras de densidad de defectos. Volúmenes de producción más grandes y una amplia variedad de productos que utilizan el mismo proceso permiten una identificación y corrección más rápidas de los problemas de densidad de defectos y de rendimiento, lo que permite a TSMC optimizar los ciclos de aprendizaje de defectos. TSMC declaró que su tecnología de fabricación N2 obtuvo más cintas nuevas que los predecesores (ya que TSMC ahora corre el riesgo de producir chips N2 para teléfonos inteligentes y clientes de HPC), por lo que la curva de densidad de defectos disminuye principalmente.

El hecho de que la tasa de reducción de defectos de N2 se alinee bien con los nodos previos basados en FINFET es particularmente significativo, dados los factores de riesgo asociados con la introducción de una arquitectura de transistores completamente nueva. Sugiere que TSMC ha transferido con éxito su experiencia en el proceso de aprendizaje y gestión de defectos en la nueva era GAAFET sin grandes contratiempos (al menos en base a lo que TSMC revela).