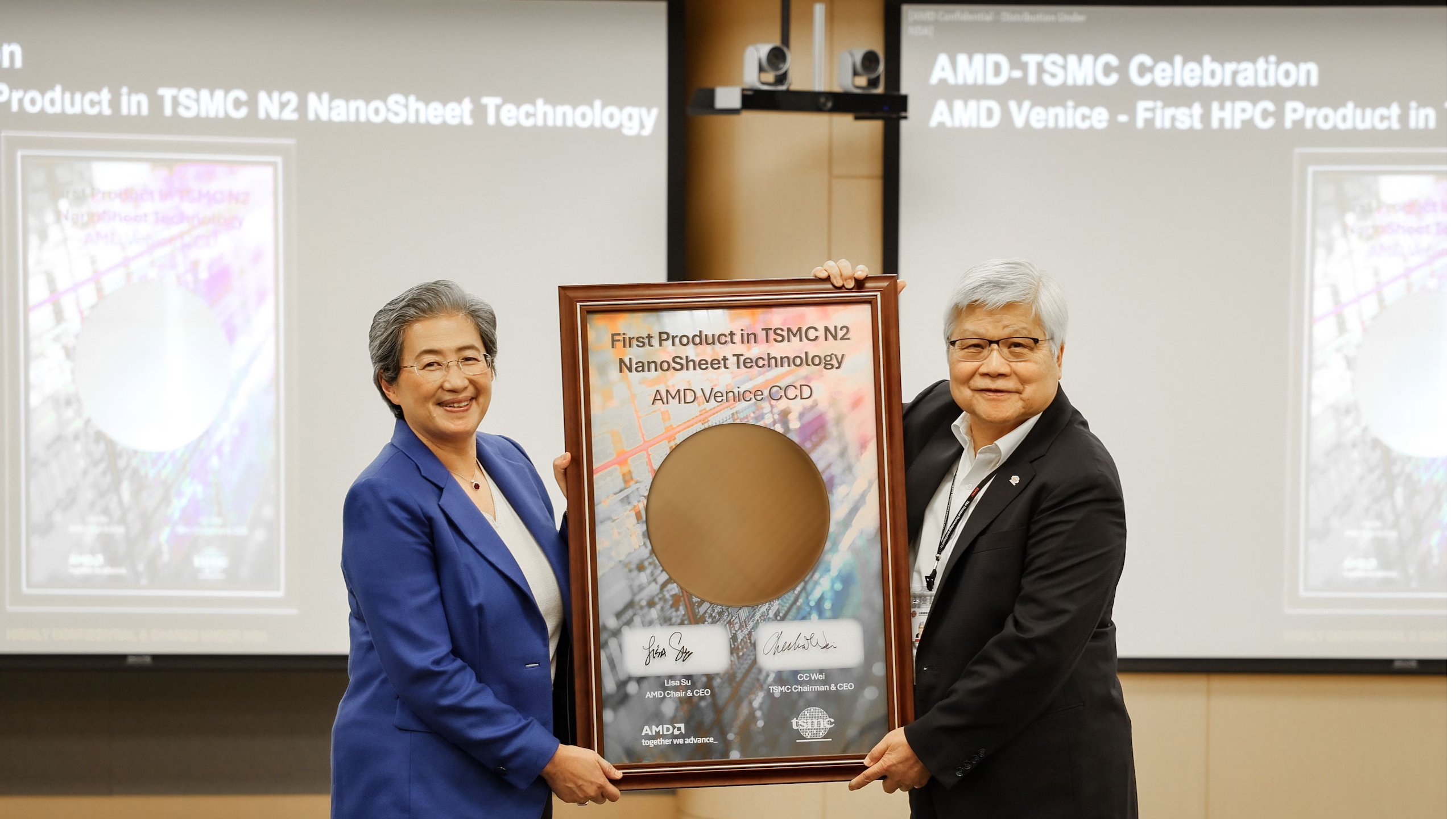

En un giro bastante inesperado de los acontecimientos, AMD anunció el lunes por la noche que había obtenido su primer silicio de 2 nm de clase, un dado de complejo central (CCD) para su procesador EPYC ‘Venice’ de sexta generación, que se espera que se lance el próximo año. El CCD de Venecia es el primer diseño de CPU HPC de la industria que se grabará en la tecnología de proceso N2 de TSMC, destacando la agresiva hoja de ruta de AMD y la preparación del nodo de producción de TSMC.

Se espera que el EPYC de sexta generación de AMD se base en la microarquitectura Zen 6 de la compañía y se espera que se lance en algún momento en 2026. La CPU dependerá de CCDS que se realizará en el proceso de fabricación N2 (Clase 2NM) de TSMC, por lo que es hora de que la compañía obtenga la primera Venice CCDS fuera del FAB. Sin embargo, el hecho de que AMD ya tiene chips de los que puede hablar destaca la larga colaboración entre AMD y TSMC, así como la culminación de los esfuerzos conjuntos para construir chips en una de las tecnologías de proceso más avanzadas que TSMC ha desarrollado hasta la fecha.

Por ahora, AMD no está discutiendo los detalles de sus procesadores o CCD de EPYC ‘Venecia’, aunque el comunicado de prensa de la compañía afirma que el silicio había sido grabado y mencionado, lo que significa que el CCD ha alimentado con éxito y ha aprobado pruebas y validación funcionales básicas.

“TSMC ha sido un socio clave durante muchos años, y nuestra profunda colaboración con sus equipos de I + D y fabricación ha permitido a AMD ofrecer constantemente productos de liderazgo que impulsan los límites de la computación de alto rendimiento”, dijo la Dra. Lisa Su, directora ejecutiva de AMD. “Ser un cliente principal de HPC para el proceso N2 de TSMC y para TSMC Arizona Fab 21 son excelentes ejemplos de cómo estamos trabajando estrechamente juntos para impulsar la innovación y entregar las tecnologías avanzadas que alimentarán el futuro de la informática”.

El N2 de TSMC es la primera tecnología de proceso de la fundición que se basa en los transistores de nanoescos de Gate-All-Around (GAA). La compañía espera que su tecnología de fabricación ofrezca una reducción del 24% al 35% en el consumo de energía o un aumento del 15% en el rendimiento a voltaje constante, junto con un aumento de 1.15x en la densidad del transistor en comparación con la generación anterior de N3 (Clase 3NM). Estas ganancias son impulsadas principalmente por el nuevo tipo de transistores y el marco de co-optimización de tecnología de diseño N2 Nanoflex N2.

El anuncio de AMD se produce después de que su archirrival Intel retrasó el lanzamiento de su procesador de Xeon ‘Clearwater Forest’ de próxima generación realizado en su tecnología de fabricación 18A (que rivaliza con el N2 de TSMC) a la primera mitad del próximo año.

Por separado, AMD anunció que ha validado con éxito el silicio de su procesador EPYC de quinta generación producido por TSMC en su instalación Fab 21 cerca de Phoenix, Arizona. Como resultado, algunas de las CPU EPYC de generación actual de la compañía ahora se pueden producir en los EE. UU.

“Estamos orgullosos de que AMD sea un cliente principal de HPC para nuestra tecnología de proceso avanzada de 2NM (N2) y TSMC Arizona FAB”, dijo el Dr. CC Wei, director ejecutivo y presidente de TSMC. “Al trabajar juntos, estamos impulsando una escala significativa de tecnología que resulta en un mejor rendimiento, eficiencia energética y rendimientos para el silicio de alto rendimiento. Esperamos continuar trabajando estrechamente con AMD para permitir la próxima era de la informática”.